## STLINK-V3MINIE debugger/programmer tiny probe for STM32 microcontrollers

### Introduction

STLINK-V3MINIE is a stand-alone debugging and programming tiny probe for STM32 microcontrollers.

The JTAG/SWD interfaces are used to communicate with any STM32 microcontroller located on an application board.

STLINK-V3MINIE also provides a Virtual COM port interface for the host PC to communicate with the target microcontroller through one UART.

STLINK-V3MINIE is a portable version easy-to-use debugger and programmer including STDC14 interface with its flat cable and on-board pads for board-to-board (BTB) card edge connector.

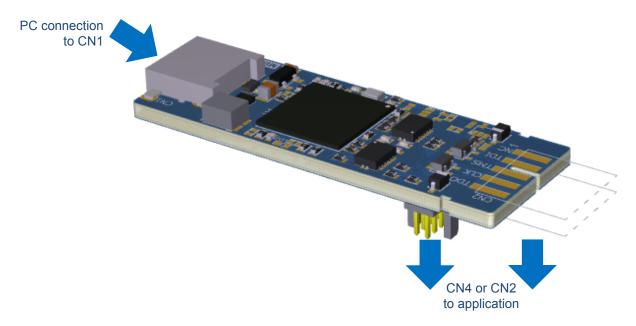

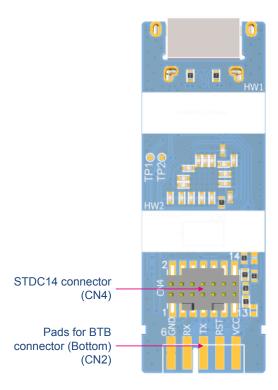

Figure 1. STLINK-V3MINIE top, bottom, and cable views

Pictures are not contractual.

## 1 Features

- Tiny 15 mm × 42 mm standalone debugging and programming probe for STM32 microcontrollers

- Self-powered through a USB Type-C<sup>®</sup> connector

- · USB 2.0 high-speed interface

- Probe firmware update through USB

- Optional drag-and-drop Flash memory programming of binary files

- Communication bi-color LED

- JTAG communication support up to 21 MHz

- SWD (Serial Wire Debug) and SWV (Serial Wire Viewer) communication support up to 24 MHz

- Virtual COM port (VCP) up to 16 Mbps

- 1.65 to 3.60 V application voltage support

- · Board connectors:

- USB Type-C<sup>®</sup> connector

- 1.27 mm pitch STDC14 debug connector with STDC14 to STDC14 flat cable

- 2.0 mm pitch on-board pads for BTB (Board-to-board) card edge connector

Note: STLINK-V3MINIE does not provide any power supply to the target application.

UM2910 - Rev 2 page 2/20

# 2 Ordering information

To order the STLINK-V3MINIE tiny probe, refer to Table 1.

**Table 1. Ordering information**

| Order code     | Content and references                                              | Description                                                                                   |

|----------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| STLINK-V3MINIE | <ul> <li>MB1762<sup>(1)</sup></li> <li>FFC<sup>(2)</sup></li> </ul> | STLINK-V3 in-circuit debugger and programmer for<br>STM32 microcontrollers with level shifter |

- 1. Tiny probe board

- 2. Flexible flat cable

UM2910 - Rev 2 page 3/20

## 3 Development environment

STLINK-V3MINIE runs with an STM32 32-bit microcontroller based on the Arm® Cortex®-M core.

Note: Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

arm

## 3.1 System requirements

- Multi-OS support: Windows<sup>®</sup> 10, Linux<sup>®</sup> 64-bit, or macOS<sup>®</sup>

- USB Type-A or USB Type-C<sup>®</sup> to USB Type-C<sup>®</sup> cable

Note: macOS<sup>®</sup> is a trademark of Apple Inc., registered in the U.S. and other countries and regions.

Linux<sup>®</sup> is a registered trademark of Linus Torvalds.

All other trademarks are the property of their respective owners.

## 3.2 Development toolchains

- IAR Systems<sup>®</sup> IAR Embedded Workbench<sup>®(1)</sup>

- Keil® MDK-ARM(1)

- STMicroelectronics STM32CubeIDE

- 1. On Windows® only.

## 3.3 Firmware upgrade

The STLINK-V3MINIE tiny probe embeds firmware that needs to be frequently updated from the *www.st.com* website to benefit from new functionality or corrections. Refer to the technical note *Overview of ST-LINK derivatives* (TN1235) for details.

UM2910 - Rev 2 page 4/20

## 4 Quick start

This section describes how to start development quickly using STLINK-V3MINIE.

Before installing and using these products, accept the Evaluation Product License Agreement from the www.st.com/epla web page.

The STLINK-V3MINIE tiny probe is a stand-alone debugging and programming probe for STM32 microcontrollers:

- It supports JTAG and SWD protocols to communicate with any STM32 microcontroller.

- It provides a Virtual COM port interface allowing the host PC to communicate with the target microcontroller through one UART

To start using STLINK-V3MINIE, follow the steps below:

- 1. Check that the STDC14 to STDC14 flat cable is present inside the box.

- 2. Install or update the IDE or STM32CubeProgrammer (STM32CubeProg) to support the STLINK-V3MINIE with the necessary drivers.

- 3. Connect the flat cable or BTB card edge connector between STLINK-V3MINIE and the application.

- 4. Connect a USB Type-A to USB Type-C® cable between STLINK-V3MINIE and the PC.

- 5. Check that the COM LED is red.

- 6. Open the development toolchain or STM32CubeProgrammer software utility. For more details, refer to the www.st.com/stlink-v3minie website.

UM2910 - Rev 2 page 5/20

## 5 STLINK-V3MINIE functional description

#### 5.1 STLINK-V3MINIE overview

STLINK-V3MINIE is a stand-alone debugging and programming tiny probe for the STM32 microcontrollers. The product supports many functions and protocols for debugging, programming, or communicating with one or several targets.

The modules are fully powered by the PC. If the COM LED blinks red, refer to the technical note *Overview of ST-LINK derivatives* (TN1235) for details.

## 5.2 STLINK-V3MINIE frequency selection

The STLINK-V3MINIE tiny probe runs internally at three different frequencies:

- High-performance frequency

- · Standard frequency, compromising between performance and consumption

- · Low-consumption frequency

By default, STLINK-V3MINIE starts at a high-performance frequency. It is the responsibility of the toolchain provider to propose or not the frequency selection at the user level.

## 5.3 High-performance modules

The STLINK-V3MINIE tiny probe supports a high-performance configuration for STM32 microcontrollers. The working voltage range goes from 1.65 to 3.6 V. The protocols and functions supported are:

- SWD with SWO (Up to 24 MHz)

- JTAG (Up to 21 MHz)

- VCP (From 736 bps to 16 Mbps)

A double-row, 14-pin (2  $\times$  7) 1.27 mm pitch male STDC14 connector is located in STLINK-V3MINIE for connection to the application target. An STDC14 to STDC14 flat cable is included in the packaging.

### 5.4 Hardware layout

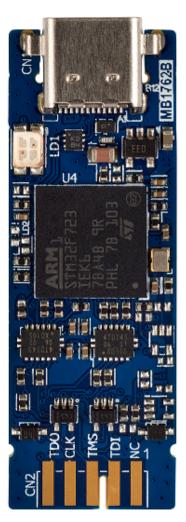

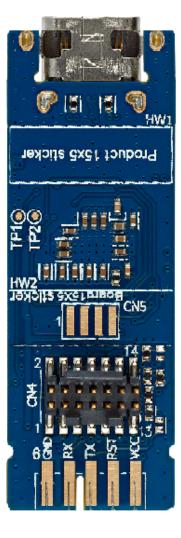

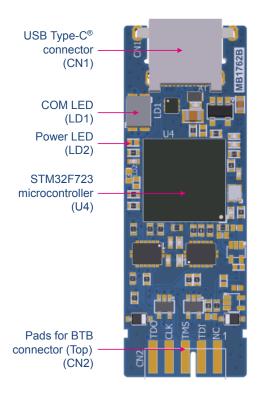

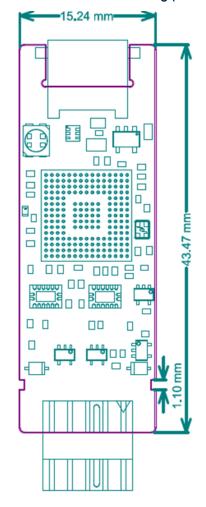

The STLINK-V3MINIE tiny probe is designed around the STM32F723 microcontroller. Figure 2 shows STLINK-V3MINIE. Figure 3 and Figure 4 show MB1762 top and bottom layouts, as MB1762 is the common board reference for STLINK-V3MINIE.

Figure 2. STLINK-V3MINIE hardware board

UM2910 - Rev 2 page 6/20

Figure 3. MB1762 top layout

Figure 4. MB1762 bottom layout

UM2910 - Rev 2 page 7/20

Figure 5. MB1762 mechanical drawing (in millimeters)

UM2910 - Rev 2 page 8/20

### 5.5 STLINK-V3MINIE functions

All functions are designed for high performance. All signals are 1.65 to 3.6 V compatible. The following description concerns STLINK-V3MINIE except for some mentioned sections and indicates where to find the functions on the boards and connectors.

#### 5.5.1 SWD with SWV

SWD protocol is a debugging and programming protocol used for STM32 microcontrollers with SWV as a trace. The signals may perform up to 24 MHz. This function is available on the CN4 connector or the CN2 pad.

#### 5.5.2 JTAG

JTAG protocol is a debugging and programming protocol used for STM32 microcontrollers. The signals may perform up to 21 MHz. This function is available on the CN4 connector or the CN2 pad.

## 5.5.3 Virtual COM port (VCP)

The serial interface VCP is directly available as a Virtual COM port of the PC, connected to the STLINK-V3MINIE CN1 USB connector. This function may be used for STM32 microcontrollers. The signals may perform from 736 bps to 16 Mbps. This function is available on the CN4 connector or the CN2 pad.

For details regarding baud rates, refer to section 14.2. of the user manual *STLINK-V3SET debugger/programmer* for *STM8* and *STM32* (UM2448).

### 5.5.4 Mass-storage interface

STLINK-V3MINIE implements a virtual mass-storage interface allowing the programming of an STM32 target Flash memory with drag-and-drop action of a binary file from a file explorer. This ability requires the STLINK-V3MINIE tiny probe to identify the connected target before enumerating it on the USB host. As a consequence, this functionality is available only if the target is connected to the STLINK-V3MINIE tiny probe when it powers up.

The mass storage interface may be disabled or enabled again by reprogramming the ST-LINK firmware. This can be performed with the *STLinkUpgrade* application. Activate the *<change type> checkbox* then select the firmware with or without mass storage and launch the update. The action is reversible.

#### 5.5.5 LEDs

Power LED: This green light indicates that 5 V is enabled (Not fitted as default).

COM LED: Refer to the technical note Overview of ST-LINK derivatives (TN1235) for details.

UM2910 - Rev 2 page 9/20

## 6 Board connectors

### 6.1 Connectors

Per convention, refer to Table 2 for I/O type definition:

Table 2. I/O type definition

| Туре | Definition           |

|------|----------------------|

| S    | Supply pin           |

| I    | Input-only pin       |

| 0    | Output-only pin      |

| I/O  | Input and output pin |

## 6.2 Pads on board to CN2 BTB card edge connector

The pads on the board have the same function as the STDC14 connector. The user can select a BTB card edge connector to connect STLINK-V3MINIE and the target board. The board-to-board card edge connector reference is 009159010061911 from AVX.

Table 3. Pads on board to CN2 BTB card edge connector

| Side   | Pin number | Pin description             | Туре |

|--------|------------|-----------------------------|------|

|        | 1          | Reserved <sup>(1)</sup>     | -    |

|        | 2          | T_JTDI/NC <sup>(2)</sup>    | 0    |

| TOP    | 3          | T_JTMS/T_SWDIO              | I/O  |

|        | 4          | T_JCLK/T_SWCLK              | 0    |

|        | 5          | T_JTDO/T_SWO <sup>(3)</sup> | I    |

|        | 6          | GND                         | S    |

|        | 7          | T_VCP_RX                    | 0    |

| воттом | 8          | T_VCP_TX                    | I    |

|        | 9          | T_NRST                      | 0    |

|        | 10         | T_VCC                       | I    |

- 1. Do not connect on target.

- 2. NC means not required for SWD (Serial Wire Debug) connection.

- 3. SWO (Serial Wire Output) is optional, and only required for SWV (Serial Wire Viewer) trace.

UM2910 - Rev 2 page 10/20

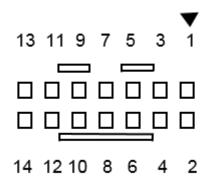

## 6.3 CN4 STDC14 connector

The CN4 STDC14 connector allows the connection to an STM32 target using the JTAG or SWD protocol, respecting from pin 3 to pin 12 the MIPI-10 (Arm® Cortex® debugging connector) pinout. It also advantageously provides two UART signals for the Virtual COM port. The related pinout for the STDC14 connector is listed in Table 4.

Figure 6. CN4 STDC14 connector (Top view)

Table 4. CN4 STDC14 connector pinout

| STDC14 pin<br>number | MIPI-10 pin<br>number | Pin description             | Туре |

|----------------------|-----------------------|-----------------------------|------|

| 1                    | -                     | Reserved <sup>(1)</sup>     | -    |

| 2                    | -                     | Reserved <sup>(1)</sup>     | -    |

| 3                    | 1                     | T_VCC                       | I    |

| 4                    | 2                     | T_JTMS/T_SWDIO              | I/O  |

| 5                    | 3                     | GND                         | S    |

| 6                    | 4                     | T_JCLK/T_SWCLK              | 0    |

| 7                    | 5                     | GND                         | S    |

| 8                    | 6                     | T_JTDO/T_SWO <sup>(2)</sup> | I    |

| 9                    | 7                     | T_JRCLK                     | I    |

| 10                   | 8                     | T_JTDI/NC <sup>(3)</sup>    | 0    |

| 11                   | 9                     | GNDDETECT                   | 0    |

| 12                   | 10                    | T_NRST                      | 0    |

| 13                   | -                     | T_VCP_RX                    | 0    |

| 14                   | -                     | T_VCP_TX                    | I    |

- 1. Do not connect on target.

- 2. SWO is optional, required only for Serial Wire Viewer (SWV) trace.

- 3. NC means not required for SWD connection.

UM2910 - Rev 2 page 11/20

## 7 Performance figures

Table 5 gives an overview of the achievable maximal performances with STLINK-V3MINIE on different communication channels. Those performances are also depending on the overall system context (target included), so they are not guaranteed to be always reachable. For instance, a noisy environment or the connection quality can impact system performance.

Table 5. Achievable maximal performance with STLINK-V3MINIE on different channels

| Board          | Target voltage | Maximum frequency (in MHz) |      |     |     |

|----------------|----------------|----------------------------|------|-----|-----|

| Board          | rarget voltage | SWD                        | JTAG | SWV | VCP |

| STLINK-V3MINIE | 3.3 V          | 24                         | 21   | 12  | 16  |

| STLINK-V3MINIE | 1.8 V          | 8                          | 8    | 12  | 12  |

UM2910 - Rev 2 page 12/20

## 8 STLINK-V3MINIE board information

## 8.1 Product marking

The stickers located on the top or bottom side of the PCB provide product information:

- Product order code and product identification for the first sticker

- Board reference with revision, and serial number for the second sticker

On the first sticker, the first line provides the product order code, and the second line the product identification.

On the second sticker, the first line has the following format: "MBxxxx-Variant-yzz", where "MBxxxx" is the board reference, "Variant" (optional) identifies the mounting variant when several exist, "y" is the PCB revision and "zz" is the assembly revision, for example B01. The second line shows the board serial number used for traceability.

Evaluation tools marked as "ES" or "E" are not yet qualified and therefore not ready to be used as reference design or in production. Any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering sample tools as reference designs or in production.

"E" or "ES" marking examples of location:

- On the targeted STM32 that is soldered on the board (For an illustration of STM32 marking, refer to the STM32 datasheet "Package information" paragraph at the <a href="https://www.st.com">www.st.com</a> website).

- · Next to the evaluation tool ordering part number that is stuck or silk-screen printed on the board.

## 8.2 STLINK-V3MINIE product history

### 8.2.1 Product identification LKV3MINIE\$KT1

This product identification is based on the MB1762 revision B-01.

#### **Product limitation**

To ensure compliance to radiated emission a USB cable featuring a ferrite clamp (magnetic ring) is mandatory.

### 8.3 Board revision history

#### 8.3.1 Board MB1762 revision B-01

The revision B-01 of the MB1762 board is the first official version.

#### **Board limitation**

No limitation identified for this board revision.

UM2910 - Rev 2 page 13/20

## 9 Federal Communications Commission (FCC) and Innovation, Science and Economic Development Canada (ISED) Compliance Statements

## 9.1 FCC Compliance Statement

#### Part 15.19

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) this device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

#### Part 15.21

Any changes or modifications to this equipment not expressly approved by STMicroelectronics may cause harmful interference and void the user's authority to operate this equipment.

#### Part 15.105

This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his own expense.

#### Responsible party (in the USA)

Terry Blanchard

Americas Region Legal | Group Vice President and Regional Legal Counsel, The Americas STMicroelectronics, Inc.

750 Canyon Drive | Suite 300 | Coppell, Texas 75019

USA

Telephone: +1 972-466-7845

### 9.2 ISED Compliance Statement

This device complies with FCC and ISED Canada RF radiation exposure limits set forth for general population for mobile application (uncontrolled exposure). This device must not be collocated or operating in conjunction with any other antenna or transmitter.

#### **Compliance Statement**

Notice: This device complies with ISED Canada licence-exempt RSS standard(s). Operation is subject to the following two conditions: (1) this device may not cause interference, and (2) this device must accept any interference, including interference that may cause undesired operation of the device.

ISED Canada ICES-003 Compliance Label: CAN ICES-3 (A) / NMB-3 (A).

#### Déclaration de conformité

Avis: Le présent appareil est conforme aux CNR d'ISDE Canada applicables aux appareils radio exempts de licence. L'exploitation est autorisée aux deux conditions suivantes : (1) l'appareil ne doit pas produire de brouillage, et (2) l'utilisateur de l'appareil doit accepter tout brouillage radioélectrique subi, même si le brouillage est susceptible d'en compromettre le fonctionnement.

Étiquette de conformité à la NMB-003 d'ISDE Canada: CAN ICES-3 (A) / NMB-3 (A).

UM2910 - Rev 2 page 14/20

## **Revision history**

Table 6. Document revision history

| Date        | Version | Changes                                                                                                                                                                                                            |

|-------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20-Oct-2021 | 1       | Initial release.                                                                                                                                                                                                   |

| 19-Jan-2022 | 2       | Added:  Performance figures  Updated:  Features  Ordering information  Section 3.3 Firmware upgrade  Figure 2, Figure 3, Figure 4, and Figure 5  Section 5.5.4 Mass-storage interface  Removed USB Type-C® section |

UM2910 - Rev 2 page 15/20

## **Contents**

| 1   | Feat | tures              |                                                                                                    | 2  |  |

|-----|------|--------------------|----------------------------------------------------------------------------------------------------|----|--|

| 2   | Ord  | dering information |                                                                                                    |    |  |

| 3   | Dev  | elopme             | nt environment                                                                                     | 4  |  |

|     | 3.1  | Syster             | m requirements                                                                                     | 4  |  |

|     | 3.2  | Develo             | opment toolchains                                                                                  | 4  |  |

|     | 3.3  | Firmw              | are upgrade                                                                                        | 4  |  |

| 4   | Quid | ck start           |                                                                                                    | 5  |  |

| 5   | STL  | INK-V3I            | MINIE functional description                                                                       | 6  |  |

|     | 5.1  | STLIN              | K-V3MINIE overview                                                                                 | 6  |  |

|     | 5.2  | STLIN              | K-V3MINIE frequency selection                                                                      | 6  |  |

|     | 5.3  | High-p             | performance modules                                                                                | 6  |  |

|     | 5.4  | Hardw              | vare layout                                                                                        | 6  |  |

|     | 5.5  | STLIN              | K-V3MINIE functions                                                                                | 9  |  |

|     |      | 5.5.1              | SWD with SWV                                                                                       | 9  |  |

|     |      | 5.5.2              | JTAG                                                                                               | 9  |  |

|     |      | 5.5.3              | Virtual COM port (VCP)                                                                             | 9  |  |

|     |      | 5.5.4              | Mass-storage interface                                                                             |    |  |

|     |      | 5.5.5              | LEDs                                                                                               | 9  |  |

| 6   | Boa  | rd conn            | ectors                                                                                             | 10 |  |

|     | 6.1  | Conne              | ectors                                                                                             | 10 |  |

|     | 6.2  |                    | on board to CN2 BTB card edge connector                                                            |    |  |

|     | 6.3  | CN4 S              | TDC14 connector                                                                                    | 11 |  |

| 7   | Perf | ormano             | e figures                                                                                          | 12 |  |

| 8   | STL  | INK-V3I            | MINIE board information                                                                            | 13 |  |

|     | 8.1  | Produ              | ct marking                                                                                         | 13 |  |

|     | 8.2  | STLIN              | K-V3MINIE product history                                                                          | 13 |  |

|     |      | 8.2.1              | Product identification LKV3MINIE\$KT1                                                              | 13 |  |

|     | 8.3  | Board              | revision history                                                                                   | 13 |  |

|     |      | 8.3.1              | Board MB1762 revision B-01                                                                         | 13 |  |

| 9   |      |                    | mmunications Commission (FCC) and Innovation, Science and Ecnt Canada (ISED) Compliance Statements |    |  |

|     | 9.1  | •                  | Compliance Statement                                                                               |    |  |

|     | 9.2  |                    | Compliance Statement                                                                               |    |  |

| Rev |      |                    |                                                                                                    |    |  |

| _   |      |                    |                                                                                                    | _  |  |

| List of tables  | 18 |

|-----------------|----|

| list of figures | 10 |

## **List of tables**

| Table 1. | Ordering information                                                     | . 3 |

|----------|--------------------------------------------------------------------------|-----|

| Table 2. | I/O type definition                                                      | 10  |

| Table 3. | Pads on board to CN2 BTB card edge connector                             | 10  |

| Table 4. | CN4 STDC14 connector pinout                                              | 11  |

| Table 5. | Achievable maximal performance with STLINK-V3MINIE on different channels | 12  |

| Table 6. | Document revision history                                                | 15  |

UM2910 - Rev 2 page 18/20

# **List of figures**

| Figure 1. | STLINK-V3MINIE top, bottom, and cable views | 1  |

|-----------|---------------------------------------------|----|

| Figure 2. | STLINK-V3MINIE hardware board               | 6  |

| Figure 3. | MB1762 top layout                           | 7  |

| Figure 4. | MB1762 bottom layout                        | 7  |

| Figure 5. | MB1762 mechanical drawing (in millimeters)  | 8  |

| Figure 6. | CN4 STDC14 connector (Top view)             | 11 |

UM2910 - Rev 2 page 19/20

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2022 STMicroelectronics - All rights reserved

UM2910 - Rev 2 page 20/20